## **Zebra Rapixo CL Pro**™

Installation and Hardware Reference

## Copyrights, Trademarks, Patents, Limitations of Liability, and Disclaimers

This section lists copyrights, acknowledgments, patent notices, limitations of liability, and disclaimers.

#### Copyright

- © 2020-2023 Zebra Technologies Corp. and/or its affiliates.

- 3 Overlook Point, Lincolnshire, Illinois 60069, USA

#### **Proprietary Statement**

This manual contains proprietary information of Zebra Technologies Corporation and its subsidiaries ("Zebra Technologies"). It is intended solely for the information and use of parties operating and maintaining the equipment described herein. Such proprietary information may not be used, reproduced, or disclosed to any other parties for any other purpose without the express, written permission of Zebra Technologies.

#### **Trademarks**

ZEBRA and the stylized Zebra head are trademarks of Zebra Technologies Corp., registered in many jurisdictions worldwide. All other trademarks are the property of their respective owners.

#### **Patents**

This product may be protected by one or more patents.

Patents: www.zebra.com/patents.

#### **Limitations of Liability**

In no event will Zebra or its suppliers be liable for any indirect, special, incidental, economic, cover or consequential damages arising out of the use of or inability to use the product, user documentation or related technical support, including without limitation, damages or costs relating to the loss of profits, business, goodwill, even if advised of the possibility of such damages. In no event will Zebra and its suppliers' liability exceed the amount paid by you, for the product.

Because some jurisdictions do not allow the exclusion or limitation of liability for consequential or incidental damages, the above limitation may not apply to you.

#### **Product Improvements**

Continuous improvements of products is a policy of Zebra Technologies. All specifications and designs are subject to change without notice.

#### **Disclaimer**

Zebra reserves the right to make changes in specifications at any time and without notice. The information provided by this document is believed to be accurate and reliable. However, neither Zebra nor its suppliers assume any responsibility for its use; or for any infringements of patents or other rights of third parties resulting from its use. No license is granted under any patents or patent right of Zebra.

#### **Publication Date**

August 11, 2023

### **Contents**

| Chapter 1: Introduction                         | 7  |  |  |  |

|-------------------------------------------------|----|--|--|--|

| Acquisition with Zebra Rapixo CL Pro8           |    |  |  |  |

| General acquisition features                    |    |  |  |  |

| Processing capabilities                         |    |  |  |  |

| Additional functionality                        |    |  |  |  |

| On-board memory                                 |    |  |  |  |

| Data transfer                                   |    |  |  |  |

| Documentation conventions                       |    |  |  |  |

| Software                                        |    |  |  |  |

| Essentials to get started                       |    |  |  |  |

| Inspecting the Zebra Rapixo CL Pro package      |    |  |  |  |

| Standard items                                  |    |  |  |  |

| Available separately                            |    |  |  |  |

| Handling components                             |    |  |  |  |

| Installation                                    |    |  |  |  |

| Need help?                                      |    |  |  |  |

| Vision Academy                                  |    |  |  |  |

| Chapter 2: Hardware installation                | 19 |  |  |  |

| Installing your Zebra Rapixo CL Pro board       |    |  |  |  |

| Installing the cable adapter bracket            |    |  |  |  |

| Connecting video sources to Zebra Rapixo CL Pro |    |  |  |  |

| Camera Link cables longer than 7 meters         |    |  |  |  |

| Chapter 3: Using multiple Zebra Rapixo CL Pro boards                  |    |  |  |  |

|-----------------------------------------------------------------------|----|--|--|--|

| Installation of multiple boards                                       |    |  |  |  |

| Simultaneous image capture from different boards                      |    |  |  |  |

| Chapter 4: Zebra Rapixo CL Pro hardware reference                     | 31 |  |  |  |

| Zebra Rapixo CL Pro hardware reference                                |    |  |  |  |

| Zebra Rapixo CL Pro acquisition                                       |    |  |  |  |

| Performance                                                           |    |  |  |  |

| Acquisition                                                           |    |  |  |  |

| Supported video sources                                               |    |  |  |  |

| Communication                                                         |    |  |  |  |

| UARTs                                                                 |    |  |  |  |

| Acquisition Controller                                                |    |  |  |  |

| Auxiliary signals                                                     |    |  |  |  |

| Camera control and auxiliary signals for Zebra Rapixo CL Pro DB/QB 41 |    |  |  |  |

| Camera control and auxiliary signals for Zebra Rapixo CL Pro SF/DF 45 |    |  |  |  |

| Specifications of the auxiliary signals49                             |    |  |  |  |

| Timers                                                                |    |  |  |  |

| Trigger                                                               |    |  |  |  |

| Quadrature decoder52                                                  |    |  |  |  |

| User signals                                                          |    |  |  |  |

| On-board memory                                                       |    |  |  |  |

| Data conversion                                                       |    |  |  |  |

| Processing FPGA                                                       |    |  |  |  |

| Possible processing operations57                                      |    |  |  |  |

| Host interface                                                        |    |  |  |  |

| Appendix A: Glossary                              | 59 |

|---------------------------------------------------|----|

| Glossary                                          |    |

| Appendix B: Technical information                 | 65 |

| Board summary                                     |    |

| Global information                                |    |

| Technical features of Zebra Rapixo CL Pro         |    |

| Electrical specifications                         |    |

| Dimensions and environmental specifications       |    |

| Connectors on Zebra Rapixo CL Pro boards          |    |

| Camera Link video input connectors                |    |

| External auxiliary I/O connectors                 |    |

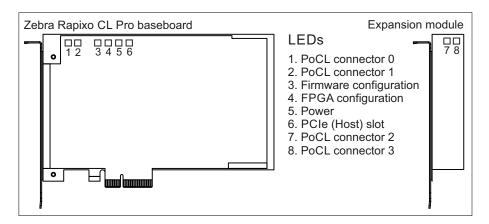

| LEDs on Zebra Rapixo CL Pro84                     |    |

| PoCL LEDs. 84                                     |    |

| Board status LEDs                                 |    |

| Appendix C: Acknowledgments                       | 87 |

| UART copyright information                        |    |

| Appendix D: Listing of Zebra Rapixo CL Pro boards | 89 |

| Key feature changes                               |    |

# Chapter

### Introduction

This chapter briefly describes the features of the Zebra Rapixo CL Pro boards, as well as the software that can be used with the boards.

#### **Acquisition with Zebra Rapixo CL Pro**

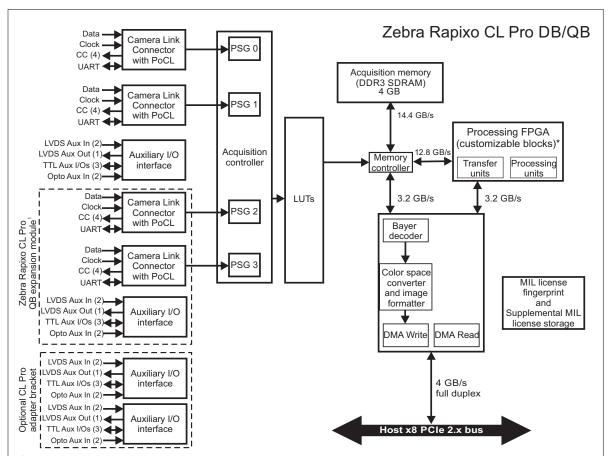

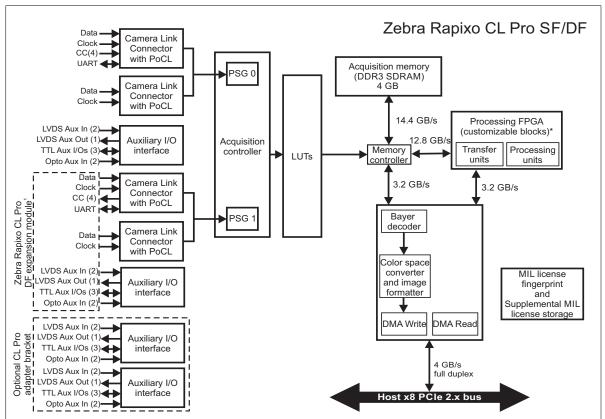

Zebra Rapixo CL Pro is a high-performance PCIe frame grabber that acquires images from video sources compliant with the Camera Link 2.1 specification (or earlier). Zebra Rapixo CL Pro also comes with FPGA-based processing-offload capabilities (a Processing FPGA).

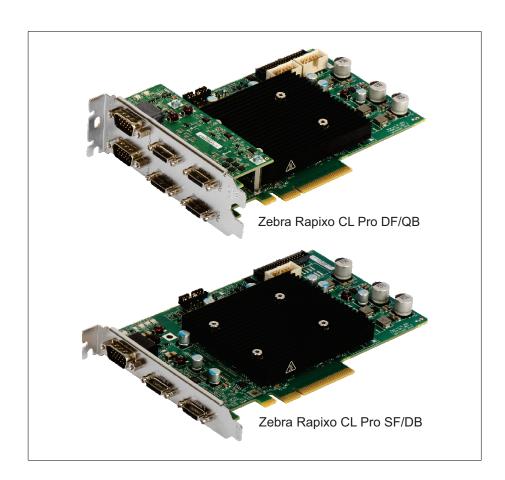

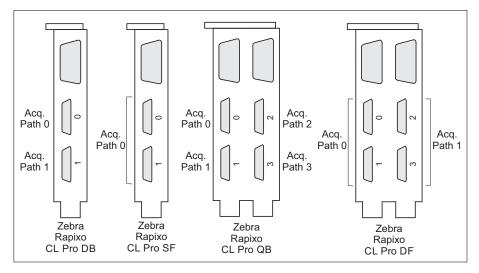

There are four versions of Zebra Rapixo CL Pro: Zebra Rapixo CL Pro SF, Zebra Rapixo CL Pro DF, Zebra Rapixo CL Pro DB, and Zebra Rapixo CL Pro QB. Zebra Rapixo CL Pro DB and QB support acquisition from Camera Link video sources in Base configuration; DB supports simultaneous acquisition from two of these video sources and QB supports four simultaneously. Zebra Rapixo CL Pro SF and DF support acquisition from Camera Link video sources in Medium, Full, 72-bit, or 80-bit configuration; SF supports acquisition from one of these video sources and DF supports two simultaneously.

Zebra Rapixo CL Pro supports power-over-Camera Link (PoCL) compliant video sources and Camera Link frequencies of 20 MHz to 85 MHz.

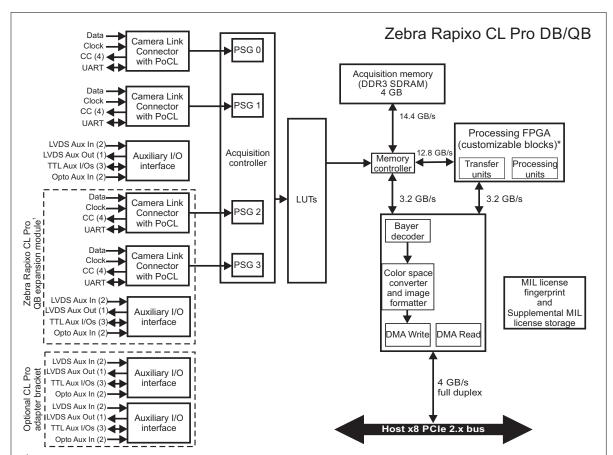

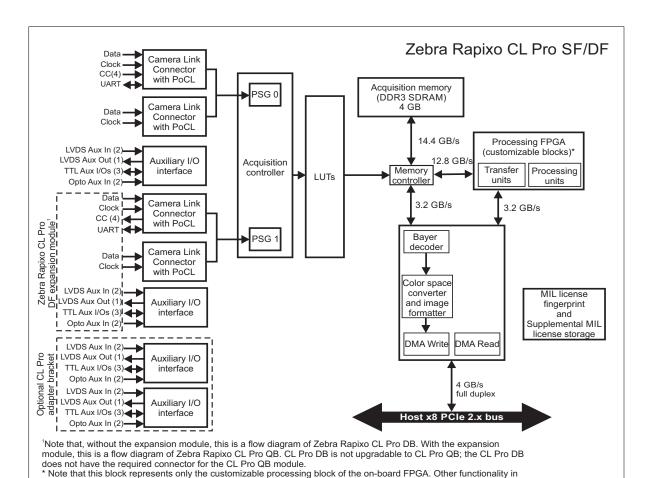

Note that, without the expansion module, this is a flow diagram of Zebra Rapixo CL Pro DB. With the expansion module, this is a flow diagram of Zebra Rapixo CL Pro QB. CL Pro DB is not upgradable to CL Pro QB; the CL Pro DB does not have the required connector for the CL Pro QB module.

<sup>\*</sup> Note that this block represents only the customizable processing block of the on-board FPGA. Other functionality in this diagram is also implemented using the FPGA.

#### **General acquisition features**

this diagram is also implemented using the FPGA.

Zebra Rapixo CL Pro supports frame-scan (area-scan) and line-scan, monochrome and color video sources. The color video sources can be RGB video sources or video sources with a Bayer color filter. Zebra Rapixo CL Pro can decode Bayer color-encoded images and perform color space conversions while transferring the image to the Host.

#### **Processing capabilities**

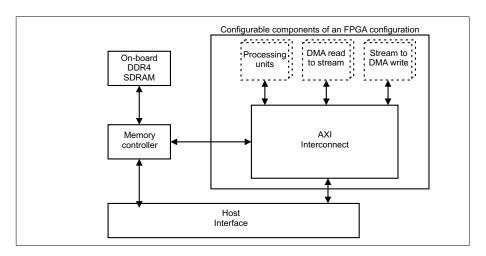

Zebra Rapixo CL Pro features an on-board real-time processing FPGA device (Processing FPGA), which can be configured to offload and even accelerate the most compute-intensive part of typical image processing applications, without generating additional data traffic within the host computer (Host).

Processing FPGA

The Processing FPGA on Zebra Rapixo CL Pro is a highly customizable Xilinx Kintex 7 FPGA\*. The operations performed on-board are controlled using MIL application-development software. Using MIL, the processing units (PUs) of an FPGA configuration can be rearranged to perform the operations in the required sequence, without having to necessarily generate a new FPGA configuration. You would typically use standard Zebra FPGA configurations. You can also chose to implement processing on your own, using the Zebra FPGA Development Kit (FDK) and C++, or you can employ Zebra's FPGA design services to generate an application-specific FPGA configuration.

Before the Processing FPGA can process grabbed images, they must be stored in on-board memory. If images stored in Host memory are required, they can be streamed directly to the Processing FPGA for processing. Images and other data resulting from processing can be stored in on-board memory or streamed to the Host.

#### **Additional functionality**

In addition to the core video capture capabilities, Zebra Rapixo CL Pro incorporates a variety of features to simplify overall system integration. These features include:

- Color space converter and image formatter. This can convert data as it is being transferred to the Host. It can convert 8- or 16-bit monochrome or 24- or 48-bit packed BGR data to monochrome, packed BGR, packed BGRa, planar RGB, or YUV (YUYV) format. In addition, it can flip or subsample data sent to the Host.

- Bayer decoder. This can convert Bayer-encoded data to RGB using an average demosaicing algorithm. The following Bayer patterns are supported: GRBG, GBRG, BGGR, and RGGB.

<sup>\*.</sup> The Processing FPGA also includes implementation for other functionality on the board, and is not used for processing only.

- Auxiliary, multi-purpose signals. These are non-video signals that can support one or more functionalities (for example, trigger input, rotary/linear encoder input, or timer output), depending on the auxiliary signal.

- Integrated quadrature decoders. These can decode input received from a rotary or linear encoder with quadrature output.

- Programmable lookup tables (LUTs). These allow Zebra Rapixo CL Pro to map data to precalculated values, before it is stored in memory.

- Zebra Rapixo CL Pro can provide 4.8 W of power per Camera Link connector to any device that supports power-over Camera Link (PoCL). This means that it can provide 4.8 W to a Base camera, or 9.6 W to a Medium or Full camera.

#### On-board memory

Zebra Rapixo CL Pro is equipped with 4 Gbytes of DDR3 SDRAM on-board memory. This memory is accessed through the memory interface, and is used to store acquired images. The memory controller has multiple input ports, and it has a maximum data transfer rate of 14.4 Gbytes/sec.

#### **Data transfer**

Your Zebra Rapixo CL Pro can send data to the Host at a maximum theoretical transfer rate of 4.0 Gbytes/sec. Optimum conditions for high speed transfer include using the board in a PCIe 2.x slot with 8 active lanes, using a 256-byte payload. DMA write performance is chipset and computer dependent, and is slightly affected by the image size and alignment in Host memory (frame start address and line pitch).

To measure the effective available bandwidth of the PCIe slot in your computer with your Zebra Rapixo CL Pro board, Zebra provides the Rapixo CL Bench tool. These tools are integrated in the MILConfigutility, which is shipped with software that supports Zebra Rapixo CL Pro (for example, MIL).

#### **Documentation conventions**

This manual refers to all Zebra Rapixo CL Pro boards as Zebra Rapixo CL Pro. When necessary, this manual distinguishes between the boards using their full names. Also note that, when the term Host is used in this manual, it refers to the host computer.

#### **Software**

To operate your Zebra Rapixo CL Pro, you can use one or more Zebra software products that supports the board. These are MIL and its derivatives (for example, MIL-Lite and Matrox Intellicam). Zebra software is supported under Windows; MIL is also supported under Linux when using Zebra Rapixo CL Pro. Consult your software manual for supported versions of these operating systems.

MIL

MIL is a high-level programming library with an extensive set of optimized functions for image capture, processing, analysis, transfer, compression, display, and archiving. Image processing operations include point-to-point, statistical, spatial filtering, morphological, geometric transformation, and FFT operations. Analysis operations support camera calibration, are performed with sub-pixel accuracy, and include pattern recognition (normalized grayscale correlation and Geometric Model Finder), blob analysis, edge extraction and analysis, measurement, image registration, metrology, character recognition (template-based, and for both normal and dot-matrix text, feature-based using String Reader and SureDotOCR respectively), code recognition and grading (1D, 2D, and composite code types), bead inspection (continuous strip of material), 3D reconstruction, 3D processing, 3D analysis, classification, and color analysis.

MIL applications are easily ported to new Zebra hardware platforms and can be designed to take advantage of multi-processing and multi-threading environments.

MIL-Lite

MIL-Lite is a subset of MIL. It includes all the MIL functions for image acquisition, transfer, display control, and archiving. It also allows you to perform processing operations that are typically useful to pre-process grabbed images.

Matrox Intellicam

Matrox Intellicam is an interactive Windows program that allows for fast video source interfacing and provides interactive access to all the acquisition features of your Zebra board. Matrox Intellicam also has the ability to create custom digitizer configuration format (DCF) files, which MIL and its derivatives use to interface with specific non-standard video sources. Matrox Intellicam is included with all Zebra software products.

#### **Essentials to get started**

To begin using your Zebra Rapixo CL Pro, you must have a computer with the following:

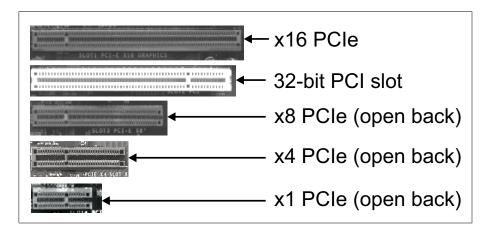

- An available conventional x8 (or x16) PCIe 2.x or 3.x slot.

- Processor with an Intel 32-bit or 64-bit architecture, or equivalent.

- A relatively up-to-date PCIe chipset. A chipset that supports the PCIe 2.x standard is preferable.

- MIL or one of its derivatives. This software should be installed after you install your board.

Zebra does not guarantee compatibility with all computers that have the above specifications. Please consult with your local Zebra representative, local Zebra sales office, the Zebra web site, or the Zebra Customer Support Group at headquarters before using a specific computer.

Consult your software package for other computer requirements (for example, operating system and memory requirements).

<sup>\*.</sup> Note that you can also install Zebra Rapixo CL Pro in a x4 PCIe slot that has a mechanical x8 connector; however, the maximum transfer rate between Zebra Rapixo CL Pro and the Host is reduced by 50%.

#### Inspecting the Zebra Rapixo CL Pro package

You should check the contents of your Zebra Rapixo CL Pro package when you first open it. If something is missing or damaged, contact your Zebra representative.

#### Standard items

You should receive the following items:

• The Zebra Rapixo CL Pro board.

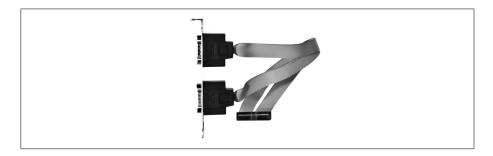

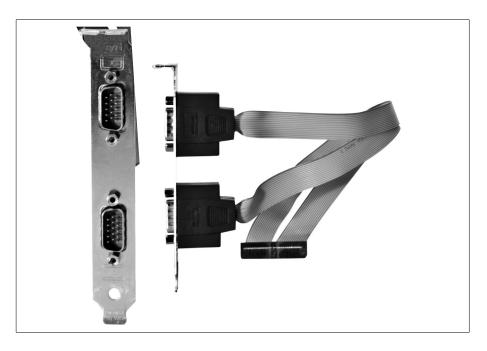

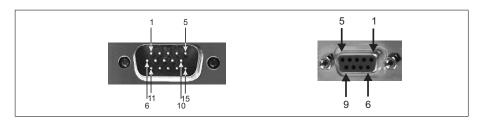

A HD-15 cable adapter bracket, equipped with two HD-15 auxiliary I/O connectors.

#### **Available separately**

You might have also ordered one or more of the following:

MIL or MIL-Lite. Matrox Intellicam is included with both of these software packages.

#### **Handling components**

The electronic circuits in your computer and the circuits on your Zebra Rapixo CL Pro are sensitive to static electricity and surges. Improper handling can seriously damage the circuits. Be sure to drain static electricity from your body by touching a metal fixture (or ground) before you touch any electronic component. In addition, do not let your clothing come in contact with the circuit boards or components.

#### Warning

Before you add or remove devices from your computer, always **turn off** the power to your computer and all peripherals.

#### Installation

The installation procedure consists of the following steps:

- 1. Complete the hardware installation procedure described in *Chapter 2: Hardware installation*.

- 2. Complete the software installation procedure described in the documentation accompanying your software package.

More information

For information on using multiple Zebra Rapixo CL Pro boards, refer to *Chapter 3: Using multiple Zebra Rapixo CL Pro boards*.

For in-depth hardware information, refer to *Chapter 4: Zebra Rapixo CL Pro hardware reference*; whereas for a summary of this information, as well as environmental and electrical specifications, and connector pinout descriptions, see *Appendix B: Technical information*.

This manual occasionally makes reference to a MIL-Lite function. However, anything that can be accomplished with MIL-Lite can also be accomplished with MIL.

#### **Need help?**

If you experience problems during installation or while using this product, you can refer to the support page on the Zebra website: supportcommunity.zebra.com/s/contactsupport?brand=matrox. The support page provides information on how to contact technical support.

To request support, you should first complete and submit the online Technical Support Request Form, accessible from the above-mentioned web page. Once you have submitted the information, a Zebra support agent will contact you shortly thereafter by email or phone, depending on the problem.

#### **Vision Academy**

The Vision Academy online training resource is also available to help customers visualize the steps involved in using various products. For access to these videos, visit the Zebra website.

# Chapter 2

## Hardware installation

This chapter explains how to install your Zebra Rapixo CL Pro board in your computer.

#### **Installing your Zebra Rapixo CL Pro board**

Before you install your Zebra Rapixo CL Pro board, some precautionary measures must be taken. Turn off the power to your computer and its peripherals, and drain static electricity from your body (by touching a metal part of the computer chassis).

Proceed with the following steps to install your board:

- 1. Remove the cover from your computer; refer to your computer's documentation for instructions.

- 2. Check that you have an empty x8 (or x16) PCIe slot in which to install your Zebra Rapixo CL Pro\*. Note that a PCIe 2.x slot and above will ensure the fastest possible transfer of data to the Host.

<sup>\*.</sup> Note that you can also install Zebra Rapixo CL Pro in a x4 PCIe slot that has a mechanical x8 connector; however, the maximum transfer rate between Zebra Rapixo CL Pro and the Host is reduced by 50%.

Zebra Rapixo CL Pro might drop frames if the PCIe slot does not have at least 8 active lanes (for example, if the board is connected to a x8 PCIe slot that has only four active lanes\*). Verify with your motherboard manufacturer to find out whether your motherboard works efficiently with a x8 PCIe board, such as Zebra Rapixo CL Pro.

If you need to install the HD-15 cable adapter bracket, you will need an additional slot. This slot need not be adjacent to the Zebra Rapixo CL Pro board. In addition, the cable adapter bracket does not plug into a slot's connector; it attaches only to the back of the computer's chassis.

\* Note that the external auxiliary I/O connectors on the cable adapter bracket are panel mount connectors. If you don't want to occupy an entire slot for the additional bracket, you can punch out two holes in the computer chassis, and then screw the connectors in the holes.

<sup>\*.</sup> After installing the board, you can verify in software the number of PCIe lanes that are currently active, using the MIL-Lite function MsysInquire() with M PCIE NUMER OF LANES.

- If there is a metal plate at the back of the selected slots, remove it. Keep the screw from the top of the plate to anchor your board and cable adapter brackets once they are installed.

- 4. Position your Zebra Rapixo CL Pro board in the selected PCIe slot. Align the connectors of your board with the opening at the back of the slot, and move the board until the connectors pass through the opening.

#### **Important**

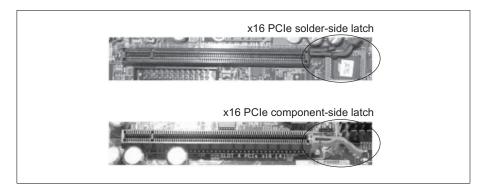

When installing your Zebra Rapixo CL Pro board in a x16 PCIe slot, special care must be taken to avoid damaging the board. Some x16 PCIe slots have a connector with a retainer. You should avoid touching the latch of this retainer with the board. Alternatively, you can remove the latch from the retainer.

- 5. Once the input connectors are in the opening of the chassis, press the board firmly but carefully straight down into the connector of the slot.

- 6. Anchor the board using the screw that you removed in step 3.

- 7. If required, install the cable adapter brackets, as described in the section *Installing the cable adapter bracket*, later in this chapter.

- 8. Attach your video sources, as described in the section *Connecting video sources to Zebra Rapixo CL Pro*, later in this chapter.

- 9. Turn on your computer.

- When you boot your computer under Windows, Windows' Plug-and-Play system will detect a new Multimedia Video Device and you will be asked to assign it a driver. At this point, you should click on Cancel.

Under Windows and Linux, the driver will be installed during the installation of Zebra Rapixo CL Pro software.

- 10. Disable active state power management (ASPM) for PCIe devices, to maximize the performance of Zebra Rapixo CL Pro. In the BIOS, disable all ASPM (or equivalent) settings (typically accessible from the Power management sub-menu of the Advanced Configurations menu). In addition, if the operating system has an ASPM for PCIe devices option, disable this option as well. For example, under Microsoft Windows 10, open the Power dialog box from the Windows Control Panel. For the currently selected power plan, click on Change Plan Settings and then click on Change Advanced Power Settings. In the presented dialog, expand PCI Express, and then expand Link State Power Management and set it to Off.

- 11. Under Microsoft Windows, set the power plan option to high performance to maximize the performance of Zebra Rapixo CL Pro and minimize the possibility of dropped frames. For example, under Microsoft Windows 10, open the **Power Options** dialog box from the Windows Control Panel and set the power plan option to **High Performance**.

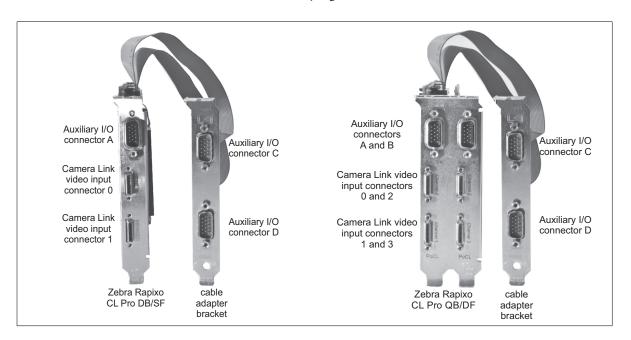

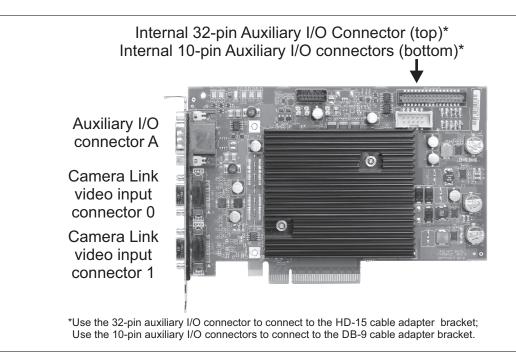

#### Installing the cable adapter bracket

To install the cable adapter bracket, proceed with the following steps:

- 1. Make sure that your Zebra Rapixo CL Pro board is fastened to the chassis.

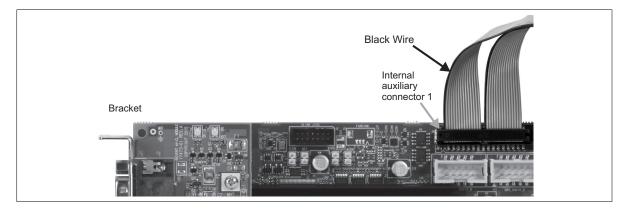

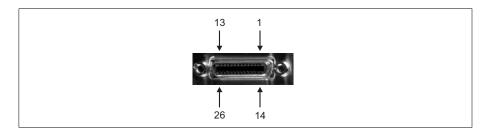

- 2. Attach the cable adapter bracket to the internal auxiliary I/O connectors on the Zebra Rapixo CL Pro board. When attaching the flat ribbon cable of the adapter bracket, position the cable so that the black wire is on the same side as the bracket of the Zebra Rapixo CL Pro board. Zebra Rapixo CL Pro has one internal 32-pin auxiliary I/O connector, and depending on the model, one or two internal 10-pin auxiliary I/O connectors. The 32-pin auxiliary I/O connector (top) is to attach the HD-15 cable adapter bracket, while the 10-pin auxiliary I/O connector (bottom) is to connect a DB-9 cable adapter bracket, if you have one available.

- 3. Slide the bracket of the cable adapter bracket into the opening at the back of the selected slot.

- 4. Anchor the bracket to the chassis using the screw that you removed in the previous section.

Note that the external auxiliary I/O connectors on the cable adapter brackets are panel mount connectors. If you don't want to occupy an entire slot for each additional bracket, you can punch out two holes in the computer chassis, and then screw the connectors in the holes.

## Connecting video sources to Zebra Rapixo CL Pro

The Zebra Rapixo CL Pro board has the following connectors on its bracket(s):

- Two or four Camera Link-compliant SDR(HDR) video input connectors. Used

to receive video input, timing, and synchronization signals, from the video source.

These are also used to transmit/receive communication signals between the video

source and the frame grabber through a UART port.

- External auxiliary I/O connector A and B (HD-15). Each used to transmit/receive auxiliary signals. Note that B is only available on Zebra Rapixo CL Pro QB and DF

To access the signals of the internal auxiliary I/O connectors, you might have installed a cable adapter bracket. It can have the following connectors:

• External auxiliary I/O connectors C and D (panel mount HD-15). Each used to transmit/receive auxiliary signals.

Attach video sources to Zebra Rapixo CL Pro as follows:

| Zebra R<br>apixo C<br>L Pro<br>board | Camera Link<br>connector O                              | Camera Link<br>connector 1              | Camera Link<br>connector 2              | Camera Link<br>connector 3              |

|--------------------------------------|---------------------------------------------------------|-----------------------------------------|-----------------------------------------|-----------------------------------------|

| DB                                   | Video source 0 in<br>Base configuration                 | Video source 1 in<br>Base configuration |                                         |                                         |

| QB                                   | Video source 0 in<br>Base configuration                 | Video source 1 in<br>Base configuration | Video source 2 in<br>Base configuration | Video source 3 in<br>Base configuration |

| SF                                   | Video source 0 in Medium, Full, or 80-bit configuration |                                         |                                         |                                         |

| DF                                   | Video source 0 in Medium, Full, or 80-bit configuration |                                         |                                         | edium, Full, or 80-bit<br>uration       |

#### Warning

❖ When connecting a video source in Medium, Full, 72-bits, or 80-bit configuration, ensure that you are connecting its cables to the appropriate connector. Accidentally connecting the cables to the wrong connector can damage the board or your video source. The Camera Link connector's pins 2-5 and pins 15-18 are output pins on the top connector (0 and 2), while they are input pins on the bottom connector (1 and 3).

To connect video sources to the Camera Link connectors, use standard Camera Link cables with a 26-pin high-density male mini Camera Link connector (HDR or SDR) at one end. When connecting to PoCL-compliant video sources, you should use PoCL-compliant Camera Link cables (HDR or SDR). Camera Link cables are not available from Zebra; for possible sources, see the *Connectors on Zebra Rapixo CL Pro boards* section in *Appendix B: Technical information*.

❖ If using both Camera Link connectors to connect to the same video source (Medium, Full, 72-bits, or 80-bits configuration), the cables you choose should be of the same type and length. Note, however, if they are not, Zebra Rapixo CL Pro will adapt to any delay caused by reasonable differences in length.

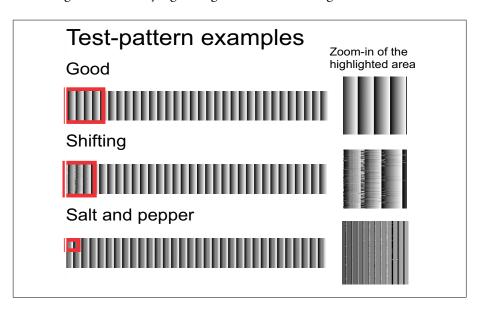

#### Camera Link cables longer than 7 meters

When using Camera Link cables that are longer than 7 meters with Zebra Rapixo CL Pro and using a pixel clock of 85 MHz, the resulting images from your camera might have either salt and pepper noise or unsynchronized lines (that is, a line is shifted either left or right, and clipped to fit the frame). These errors might be caused by signal degradation due to long cables.

To fix this problem, you must adjust your DCF. To do so:

- 1. Set your camera to generate images that contain as many different pixel values as possible for every tap (for example, a test pattern containing a horizontal ramp). Refer to your camera's documentation for more information. If your camera does not have a test-pattern mode, select an image similar to a horizontal ramp.

- 2. Once the test pattern (or sample image) is available, use the Deseralizer tool. This tool will adjust values within your DCF to compensate for signal degradation due to the long cables. This tool is available on the Rapixo CL page of the MILConfig utility. Follow all on-screen instructions.

When the process is complete, your camera's DCF is updated. Any MIL application that uses this DCF in the same physical environment should now be able to receive better images (using your camera as a video source).

Note that, if your MILConfig utility does not have the Deserializer tool, contact Zebra Technical Support for assistance.

Chapter 3

## Using multiple Zebra Rapixo CLPro boards

This chapter explains how to use multiple Zebra Rapixo CL Pro boards.

#### **Installation of multiple boards**

You can install and use multiple Zebra Rapixo CL Pro boards in one computer. Install each additional Zebra Rapixo CL Pro board as you installed the first board (refer to *Chapter 2: Hardware installation*). The number of Zebra Rapixo CL Pro boards that you can install is primarily dependent on the number of physical slots in your computer, and your BIOS; your BIOS establishes how many PCIe devices can be mapped to the PCIe memory space of your computer.

Using MIL-Lite, you have to allocate a MIL system for each board and allocate the resources of each MIL system. For more information, see MsysAlloc() with M\_SYSTEM\_RAPIXOCL in the MIL Reference.

#### Simultaneous image capture from different boards

In addition to capturing images from multiple video sources with a single Zebra Rapixo CL Pro board, you can also simultaneously capture images from video sources attached to multiple Zebra Rapixo CL Pro boards. Note that the number of video sources from which you can simultaneously capture images is limited by the PCIe chipset on your computer.

The use of a high performance PCIe chipset is necessary to sustain PCIe transfers to Host memory. Ideally, at least a PCIe 2.x chipset (or more recent) should be used. A PCIe 2.x or more recent Host bus will optimize the speed of data transmission, and will minimize data loss.

To measure the effective available bandwidth of the PCIe slot in your computer with the Zebra Rapixo CL Pro board, you can use the Rapixo CL Bench tool integrated in the MILConfig utility. As a reference point, capturing from a 2K x 2K, 8-bit, 60 frames/sec video source will require a minimum bandwidth of 240 Mbytes/sec, plus an additional bandwidth margin of approximately 20%, for a bandwidth of 288 Mbytes/sec.

Chapter

4

## **Zebra Rapixo CL Pro hardware reference**

This chapter explains the architecture, features, and modes of the Zebra Rapixo CL Pro hardware.

#### Zebra Rapixo CL Pro hardware reference

This chapter provides information on the Zebra Rapixo CL Pro hardware. It covers the architecture, features, and modes of the board's acquisition section. In addition, the chapter covers the Zebra Rapixo CL Pro hardware related to the formatting and transfer of data. A summary of the features of Zebra Rapixo CL Pro, as well as pin assignments for the various connectors, can be found in *Appendix B: Technical information*.

#### Acquisition path

This manual uses the term acquisition path to refer to a path that has the capability to, for example, capture a component or stream of the video input signal. The term independent acquisition path is used to refer to an acquisition path that can, if required, acquire data from a video source independently from another such path on the same frame grabber. On Zebra Rapixo CL Pro, there are up to four acquisition paths (depending on the model).

#### Digitizer

MIL-Lite uses the concept of a MIL digitizer to represent the acquisition path(s) with which to grab from one input source of the specified type. When several MIL digitizers are allocated, their device number along with their DCF identify if they represent the same path(s) (but perhaps for a different input format) or independent path(s) for simultaneous acquisition.

#### Digitizer configuration format

To program the acquisition section, allocate a MIL digitizer using MdigAlloc() with an appropriate DCF (supplied or created) and digitizer device number. If you find a DCF file that is suitable for your video source, but you need to adjust some of the more common settings, you can do so directly, without adjusting the file, using the appropriate MIL-Lite function. For more specialized adjustments, use the Matrox Intellicam program to adjust the DCF file.

Note that, without the expansion module, this is a flow diagram of Zebra Rapixo CL Pro DB. With the expansion module, this is a flow diagram of Zebra Rapixo CL Pro QB. CL Pro DB is not upgradable to CL Pro QB; the CL Pro DB does not have the required connector for the CL Pro QB module.

<sup>\*</sup> Note that this block represents only the customizable processing block of the on-board FPGA. Other functionality in this diagram is also implemented using the FPGA.

Note that, without the expansion module, this is a flow diagram of Zebra Rapixo CL Pro DB. With the expansion module, this is a flow diagram of Zebra Rapixo CL Pro QB. CL Pro DB is not upgradable to CL Pro QB; the CL Pro DB does not have the required connector for the CL Pro QB module.

\* Note that this block represents only the customizable processing block of the on-board FPGA. Other functionality in this diagram is also implemented using the FPGA.

#### Zebra Rapixo CL Pro acquisition

Zebra Rapixo CL Pro can capture video from digital video sources compliant with the Camera Link 2.1 specification (or earlier). Zebra Rapixo CL Pro can provide power-over-Camera Link to attached video sources.

Zebra Rapixo CL Pro supports frame-scan (area-scan) and line-scan monochrome and color video sources. The color video sources can be RGB video sources or video sources with a Bayer color filter. Zebra Rapixo CL Pro can decode Bayer color-encoded images and perform color space conversions while transferring the image to the Host. Besides standard Camera Link video sources, Zebra Rapixo CL Pro also supports additional types of video sources, including some time-multiplexed video sources.

Operating in Base configuration, Zebra Rapixo CL Pro DB has two independent acquisition paths and Zebra Rapixo CL Pro QB has four independent acquisition paths. Operating in Medium, Full, 72-bit, or 80-bit configuration, Zebra Rapixo CL Pro SF has one acquisition path and Zebra Rapixo CL Pro DF has two independent acquisition paths.

Each acquisition path can grab at Camera Link frequencies of 20 MHz to 85 MHz. Each acquisition path has its own programmable synchronization generator (PSG) and can operate at different acquisition rates.

The acquisition section of Zebra Rapixo CL Pro supports a comprehensive set of general purpose I/O and serial ports to control cameras and other devices.

#### **Performance**

The video timing of each acquisition path is as follows:

|                                                       | Maximum |

|-------------------------------------------------------|---------|

| Number of pixels / line (including sync and blanking) | 64 K    |

| Number of lines / frame (including sync and blanking) | 64 K    |

| Pixel clock                                           | 85 Mhz  |

The maximum pixel clock frequency is dependent on the length of the cable used. Refer to the Technical features of Zebra Rapixo CL Pro subsection of the Board summary section in Appendix B: Technical information.

#### **Acquisition**

A Base-type acquisition path supports up to 24 bits of video data when acquiring from Camera Link-compliant video sources or up to 48 bits when acquiring from non-standard time-multiplexed video sources. Similarly, a Medium-type acquisition path can grab up to 48 bits of video data when acquiring from Camera Link-compliant sources or up to 64 bits when acquiring from non-standard time-multiplexed sources. A Full-type acquisition path supports up to 64 bits of video data when acquiring from Camera Link-compliant video sources. An 80-bit-type acquisition path supports up to 80 bits of video data when acquiring from Camera Link-compliant video sources.

The video sources can be frame-scan (area-scan) or line-scan video sources. Note that the acquisition paths in dual-Base mode are completely independent; therefore, the video sources do not need to be identical when running in these modes.

#### **Supported video sources**

Zebra Rapixo CL Pro boards support all video sources that are Camera Link 2.1 compatible

The following are some video sources that are supported when running in Base configuration:

|                      | Video sources supported per acquisition path |

|----------------------|----------------------------------------------|

| Camera Link Standard | One tap 8/10/12/14/16-bit.                   |

|                      | Two tap 8/10/12-bit.                         |

|                      | One tap 3 x 8-bit (RGB).                     |

In addition to the above video sources, the following are some video sources that are supported when running in Medium configuration:

|                      | Video sources supported           |

|----------------------|-----------------------------------|

| Camera Link Standard | • Two tap 14/16-bit.              |

|                      | Three tap 12/14-bit.              |

|                      | • Three tap 16-bit <sup>*</sup> . |

|                      | • Four tap 8/10/12-bit.           |

|                      | Five*/six tap 8-bit.              |

<sup>\*.</sup> Due to lack of demand, these modes are not natively supported with the current driver and/or firmware; however, support could be possible with an appropriate DCF. Contact Zebra customer support to have an appropriate DCF implemented.

In addition to the above video sources, the following are some video sources that are supported when running in Full configuration:

|                      | Video sources supported        |  |

|----------------------|--------------------------------|--|

| Camera Link Standard | • Four tap 14/16-bit.          |  |

|                      | • Five */six tap 10/12-bit.    |  |

|                      | • Seven*/eight/nine tap 8-bit. |  |

<sup>\*.</sup> Due to lack of demand, these modes are not natively supported with the current driver and/or firmware; however, support could be possible with an appropriate DCF. Contact Zebra customer support to have an appropriate DCF implemented.

In addition to the above video sources, the following are some video sources that are supported when running in 72-bit configuration:

|                      | Video sources supported |

|----------------------|-------------------------|

| Camera Link Standard | Five tap 14-bit*.       |

<sup>\*.</sup> Due to lack of demand, these modes are not natively supported with the current driver and/or firmware; however, support could be possible with an appropriate DCF. Contact Zebra customer support to have an appropriate DCF implemented.

In addition to the above video sources, the following are some video sources that are supported when running in 80-bit configuration:

|                      | Video sources supported  |

|----------------------|--------------------------|

| Camera Link Standard | Five tap 16-bit*.        |

|                      | Seven*/eight tap 10-bit. |

|                      | • 10 tap 8-bit.          |

<sup>\*.</sup> Due to lack of demand, these modes are not natively supported with the current driver and/or firmware; however, support could be possible with an appropriate DCF. Contact Zebra customer support to have an appropriate DCF implemented.

Zebra Rapixo CL Pro supports power-over-Camera Link (PoCL) and externally supplied video sources. For compatibility with externally supplied video sources, Zebra Rapixo CL Pro features SafePower mode to supply power only after determining whether the connected video source is PoCL compliant. The PoCL protection on-board fuse can sustain a current of 0.4 A.

#### Communication

For each acquisition path, two LVDS pairs are used to transmit and receive asynchronous serial communication between the video source and the board. These signals are handled by the Universal Asynchronous Receiver/Transmitters (UARTs).

For each acquisition path, four camera control output signals are also available. These are general-purpose signals that are sent to the video source.

#### **UARTS**

Zebra Rapixo CL Pro offers an LVDS-compatible Zebra serial interface. Each interface is mapped as a COM port so that it can be accessed through the Microsoft Windows API. Each interface is comprised of both a transmit port and a receive port, permitting the interface to work in full-duplex (bidirectional) mode. The interfaces are located on the Camera Link connectors.

Each interface is controlled by a Universal Asynchronous Receiver-Transmitter (UART)\*. Each UART features independently programmable baud rates, supporting all standard baud rates from 300 baud up to 115200† baud.

#### **Acquisition Controller**

The acquisition controller is responsible for reconstructing and storing image data in main on-board memory. When writing data to memory, the acquisition controller can perform line and frame reversal; it can flip the image horizontally and/or vertically.

On Zebra Rapixo CL Pro DB/QB, the acquisition controller can write to four non-sequential memory regions (zones) per acquisition path.

On Zebra Rapixo CL Pro SF/DF, the acquisition controller can write to the following number of non-sequential memory regions maximum: 6 for Medium, 8 for Full, 9 for 72-bit, and 10 for 80-bit<sup>‡</sup>.

Note that the width of each region must be a multiple of the number of taps in that region.

To establish the number of non-sequential memory regions to which your video source must write, refer to the documentation accompanying your video source.

<sup>\*.</sup> The UART implementation was derived from a design by Daniel Wallner. Please see *Appendix C: Acknowledgments* for copyright information.

<sup>†.</sup> In addition, the maximum baud rate is highly dependent on the amount of computer resources available.

<sup>‡.</sup> The 10 non-sequential memory regions in 80-bit configuration are only available with 8-bit taps.

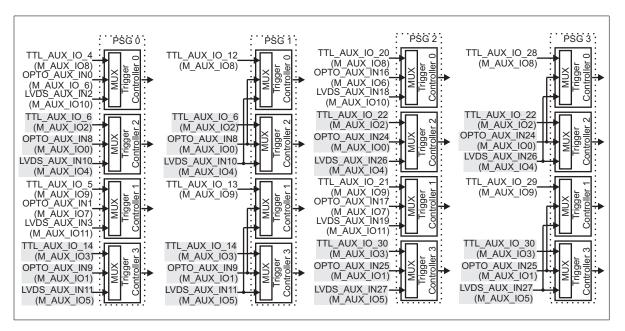

#### **PSGs**

For each acquisition path, the acquisition controller provides a programmable synchronization generator (PSG). Each PSG allows for independent acquisition from one video source, since each PSG is responsible for managing all video timing and synchronization signals.

The PSGs are also responsible for managing the camera control and auxiliary signals supported by the board. These signals are configurable signals that can support one or several functions, one of which is user-defined; the table in the next subsection identifies the functions to which the camera control and auxiliary signals can be defined. The PSGs are also responsible for implementing the functionality to which these can be defined.

# **Auxiliary signals**

The following sections describe the auxiliary signals for Zebra Rapixo CL Pro.

# Camera control and auxiliary signals for Zebra Rapixo CL Pro DB/QB

The following tables summarize the auxiliary functionality that the PSGs support, and the corresponding signals that the PSGs can receive/generate, for Zebra Rapixo CL Pro DB/QB. The table also documents the MIL constants to use.

|                                                                                  |                  | ı   | LVDS c | am. ctı               | rl  | I   | LVDS c | am. ctı               | rl  | ı   | .VDS c | am. ctı               | rl  | l   | .VDS c | am. ctr               | 1   |

|----------------------------------------------------------------------------------|------------------|-----|--------|-----------------------|-----|-----|--------|-----------------------|-----|-----|--------|-----------------------|-----|-----|--------|-----------------------|-----|

|                                                                                  |                  |     | Conn   | ra Link<br>ector<br>O |     |     |        | ra Link<br>ector<br>1 |     |     | Conn   | ra Link<br>ector<br>* |     |     |        | ra Link<br>ector<br>* |     |

| M_CC_IOn                                                                         | n                | 1   | 2      | 3                     | 4   | 1   | 2      | 3                     | 4   | 1   | 2      | 3                     | 4   | 1   | 2      | 3                     | 4   |

| for M_DEVm <sup>†</sup>                                                          | m                | 0   | 0      | 0                     | 0   | 1   | 1      | 1                     | 1   | 2   | 2      | 2                     | 2   | 3   | 3      | 3                     | 3   |

| Functionality that can be routed                                                 | Acquisition path | CC1 | CC2    | CC3                   | 664 | 661 | CC2    | cc3                   | 664 | CC1 | CC2    | CC3                   | 664 | CC1 | CC2    | ເວວ                   | CC4 |

| Timer                                                                            | 0                | 1/2 | 1/2    | 1/2                   | 1/2 |     |        |                       |     |     |        |                       |     |     |        |                       |     |

| (M_TIMERn <sup>†</sup> )                                                         | 1                |     |        |                       |     | 1/2 | 1/2    | 1/2                   | 1/2 |     |        |                       |     |     |        |                       |     |

|                                                                                  | 2                |     |        |                       |     |     |        |                       |     | 1/2 | 1/2    | 1/2                   | 1/2 |     |        |                       |     |

|                                                                                  | 3                |     |        |                       |     |     |        |                       |     |     |        |                       |     | 1/2 | 1/2    | 1/2                   | 1/2 |

| User output                                                                      | 0                | 0/1 | 0/1    | 0/1                   | 0/1 |     |        |                       |     |     |        |                       |     |     |        |                       |     |

| (bit of Camera Link static-user-output register M_USER_BIT_CC_IOn <sup>†</sup> ) | 1                |     |        |                       |     | 0/1 | 0/1    | 0/1                   | 0/1 |     |        |                       |     |     |        |                       |     |

|                                                                                  | 2                |     |        |                       |     |     |        |                       |     | 0/1 | 0/1    | 0/1                   | 0/1 |     |        |                       |     |

|                                                                                  | 3                |     |        |                       |     |     |        |                       |     |     |        |                       |     | 0/1 | 0/1    | 0/1                   | 0/1 |

<sup>\*.</sup> Only available on Zebra Rapixo CL Pro QB

<sup>†.</sup> MIL constant, where *n* and *m* correspond to the number in the row. M\_DEV*m* is the required device number of the digitizer (**MdigAlloc()**) that you must use to access this signal.

#### 42 Chapter 4: Zebra Rapixo CL Pro hardware reference

|                                              |                               | TTL Aux I/O Aux I/O Connector |              |              |               |               |               |               |               |        |               |               |               |              |              |              | PT0          |               |               |               |               |              |              |               | /DS           |               |               |               |               | LV            |                | Aux O           | ut             |

|----------------------------------------------|-------------------------------|-------------------------------|--------------|--------------|---------------|---------------|---------------|---------------|---------------|--------|---------------|---------------|---------------|--------------|--------------|--------------|--------------|---------------|---------------|---------------|---------------|--------------|--------------|---------------|---------------|---------------|---------------|---------------|---------------|---------------|----------------|-----------------|----------------|

|                                              |                               |                               |              |              | ŀ             | \ux I         | /0 0          | Conn          | ecto          | r      |               |               |               |              | ŀ            | \ux I        | /O C         | onn           | ecto          | r             |               |              | ŀ            | Aux I         | /O C          | onn           | ecto          | r             |               | ,             | Conn           | c I/O<br>nector | r              |

|                                              |                               |                               | Α            |              |               | C             |               |               | В*            |        |               | D             |               |              | A            | (            |              | В             | *             | [             | )             | -            | 4            | (             | C             | В             | *             | [             | )             | Α             | C              | B*              | D              |

| M_AUX_IOn                                    | n                             | 8                             | 9            | 2            | 8             | 9             | 3             | 8             | 9             | 2      | 8             | 9             | 3             | 6            | 7            | 0            | 1            | 6             | 7             | 0             | 1             | 10           | 11           | 4             | 5             | 10            | 11            | 4             | 5             | 12            | 12             | 13              | 13             |

| for M_DEVm <sup>†</sup>                      | m                             | 0                             | 0            | 0/1          | 1             | 1             | 0/1           | 2             | 2             | 2/3    | 3             | 3             | 2/3           | 0            | 0            | 0/1          | 0/1          | 2             | 2             | 2/3           | 2/3           | 0            | 0            | 0/1           | 0/1           | 2             | 2             | 2/3           | 2/3           | 0             | 1              | 2               | 3              |

| Functionality that can be routed or received | Acquisition path <sup>‡</sup> | TTL_AUX_10_4                  | TTL_AUX_10_5 | TTL_AUX_10_6 | TTL_AUX_10_12 | TTL_AUX_10_13 | TTL_AUX_I0_14 | TTL_AUX_10_20 | TTL_AUX_10_21 | ol_XU4 | TTL_AUX_10_28 | TTL_AUX_10_29 | TTL_AUX_10_30 | OPTO_AUX_IN0 | OPTO_AUX_IN1 | OPTO_AUX_IN8 | OPTO_AUX_IN9 | OPTO_AUX_IN16 | OPTO_AUX_IN17 | OPTO_AUX_IN24 | OPTO_AUX_IN25 | LVDS_AUX_IN2 | LVDS_AUX_IN3 | LVDS_AUX_IN10 | LVDS_AUX_IN11 | LVDS_AUX_IN18 | LVDS_AUX_IN19 | LVDS_AUX_IN26 | LVDS_AUX_IN27 | LVDS_AUX_0UT7 | LVDS_AUX_0UT15 | LVDS_AUX_0UT23  | LVDS_AUX_0UT31 |

| Timer                                        | 0                             |                               | 1            | 2            |               |               |               |               |               |        |               |               |               | Г            |              |              |              |               |               |               |               |              |              |               |               |               |               |               |               | 1/2           |                |                 |                |

| (M_TIMERn <sup>†</sup> )                     | 1                             |                               |              |              |               | 1             | 2             |               |               |        |               |               |               |              |              |              |              |               |               |               |               |              |              |               |               |               |               |               |               |               | 1/2            |                 |                |

|                                              | 2                             |                               |              |              |               |               |               |               | 1             | 2      |               |               |               |              |              |              |              |               |               |               |               |              |              |               |               |               |               |               |               |               |                | 1/2             |                |

|                                              | 3                             |                               |              |              |               |               |               |               |               |        |               | 1             | 2             |              |              |              |              |               |               |               |               |              |              |               |               |               |               |               |               | ᆫ             |                |                 | 1/2            |

| Trigger controller                           | 0                             | T0                            | T1           | T2           |               |               | T3            |               |               |        |               |               |               | T0           | T1           | T2           | T3           |               |               |               |               | T0           | T1           | T2            | _             |               |               | L             |               | ᆫ             | L              |                 |                |

| affected by                                  | 1                             |                               |              | T2           | T0            | T1            | T3            |               |               |        |               |               |               | ı            |              | TO/          | T1/<br>T3    |               |               |               |               |              |              |               |               |               |               |               |               | ı             |                |                 | ĺ              |

| input signal <sup>§</sup>                    | 2                             | -                             |              |              |               |               |               | T0            | T1            | T2     |               |               | T3            | ┢            |              | T2           | 13           | T0            | T1            | T2            | T3            |              |              | T2            | 13            | T0            | T1            | T2            | T3            | ⊢             |                | Ш               |                |

|                                              | 3                             |                               |              |              |               |               |               | 10            | 11            | T2     | T0            | T1            | T3            | -            |              |              |              | 10            | 11            | T0/           |               |              |              |               |               | 10            | 11            | _             |               |               |                |                 |                |

|                                              | ٥                             |                               |              |              |               |               |               |               |               | 12     | 10            | ' '           | 13            | ı            |              |              |              |               |               | T2            | T3            |              |              |               |               |               |               | T2            | T3            | ı             |                |                 |                |

| Timer-clock                                  | 0                             |                               |              |              |               |               |               |               |               |        |               |               |               | Г            |              |              |              |               |               |               |               |              | 0            |               |               |               |               |               |               | Г             |                |                 |                |

| input                                        | 1                             |                               |              |              |               |               |               |               |               |        |               |               |               |              |              |              |              |               |               |               |               |              |              |               | 0             |               |               |               |               | Г             |                |                 |                |

|                                              | 2                             |                               |              |              |               |               |               |               |               |        |               |               |               |              |              |              |              |               |               |               |               |              |              |               |               |               | 0             |               |               |               |                |                 |                |

|                                              | 3                             |                               |              |              |               |               |               |               |               |        |               |               |               |              |              |              |              |               |               |               |               |              |              |               |               |               |               |               | 0             | ᆫ             |                |                 |                |

| Bit of quadrature                            | 0                             |                               |              |              |               |               |               |               |               |        |               |               |               |              |              |              |              |               |               |               |               | 0            | 1            |               |               |               |               |               |               |               |                |                 |                |

| input**                                      | 1                             |                               |              |              |               |               |               |               |               |        |               |               |               | _            |              |              |              |               |               |               |               |              |              | 0             | 1             |               |               | _             |               | ┖             |                |                 |                |

|                                              | 2                             |                               |              |              |               |               |               |               |               |        |               |               |               |              |              |              |              |               |               |               |               |              |              |               |               | 0             | 1             | <u> </u>      |               | ┖             | <u> </u>       |                 |                |

|                                              | 3                             | Ļ                             |              | ļ.,          |               |               | _             |               |               |        |               |               |               | L            |              |              |              |               |               |               |               |              |              |               |               |               |               | 0             | 1             | Ļ             | _              |                 |                |

| User output (bit of main static-user-output  | 0                             | 2                             | 3            | 4            | _             | _             | 5             |               |               |        |               |               |               | _            |              |              |              |               |               |               |               |              |              |               |               |               |               | <u> </u>      | Ш             | 0             | Ļ              |                 | <u> </u>       |

| register                                     | 1                             | _                             |              | 4            | 2             | 3             | 5             | _             | _             |        |               | _             | <u> </u>      | ▙            |              |              |              |               |               |               |               | _            | _            |               |               |               |               | <u> </u>      | $\square$     | ⊢             | 0              |                 | <u> </u>       |

| M_USER_BITn <sup>†</sup> )                   | 2                             | _                             |              |              | _             | _             |               | 2             | 3             | 4      | _             | _             | 5             | ┡            |              |              |              |               |               |               | $\square$     | _            | _            |               |               |               |               | <u> </u>      | $\square$     | ⊢             | ₩              | 0               |                |

| 00EII_DII// /                                | 3                             |                               |              |              |               |               |               |               |               | 4      | 2             | 3             | 5             |              |              |              |              |               |               |               |               |              |              |               |               |               |               |               | Ш             | ட             | <u> </u>       |                 | 0              |

- \*. Zebra Rapixo CL Pro DB does not have this connector.

- †. MIL constant, where n and m correspond to the number in the row. M\_DEVm is the required device number of the digitizer (MdigAlloc()) that you must use to access this signal.

- ‡. Only Zebra Rapixo CL Pro QB has four acquisition paths. For Zebra Rapixo CL Pro DB, only information for acquisition paths 0 and 1 is applicable.

- §. Note that there are only 4 trigger controllers per acquisition path.

- \*\*. A rotary/linear encoder with quadrature output transmits a two-bit code. The table entries 0 and 1, therefore, denote bit position.

|                | path        |     |        |         |     |       |       | L   | .VDS c | am. ct | rl     |     |     |       |        |     |     |

|----------------|-------------|-----|--------|---------|-----|-------|-------|-----|--------|--------|--------|-----|-----|-------|--------|-----|-----|

|                |             |     | CL cor | nect. ( | )   | CL co | nnect | . 1 |        | CL co  | onnect | . 2 |     | CL co | onnect | . 3 |     |

| Type of signal | Acquisition | 100 | CC2    | 603     | CC4 | 100   | CC2   | 603 | CC4    | 661    | CC2    | 603 | CC4 | 100   | CC2    | 603 | CC4 |

| VSYNC output   | 0           | 1   | 1      | 1       | 1   |       |       |     |        |        |        |     |     |       |        |     |     |

|                | 1           |     |        |         |     | 1     | 1     | 1   | 1      |        |        |     |     |       |        |     |     |

|                | 2           |     |        |         |     |       |       |     |        | 1      | 1      | 1   | 1   |       |        |     |     |

|                | 3           |     |        |         |     |       |       |     |        |        |        |     |     | 1     | 1      | 1   | 1   |

| HSYNC output   | 0           | 1   | 1      | 1       | 1   |       |       |     |        |        |        |     |     |       |        |     |     |

|                | 1           |     |        |         |     | 1     | 1     | 1   | 1      |        |        |     |     |       |        |     |     |

|                | 2           |     |        |         |     |       |       |     |        | 1      | 1      | 1   | 1   |       |        |     |     |

|                | 3           |     |        |         |     |       |       |     |        |        |        |     |     | 1     | 1      | 1   | 1   |

| Clock output   | 0           | 1   | 1      | 1       | 1   |       |       |     |        |        |        |     |     |       |        |     |     |

|                | 1           |     |        |         |     | 1     | 1     | 1   | 1      |        |        |     |     |       |        |     |     |

|                | 2           |     |        |         |     |       |       |     |        | 1      | 1      | 1   | 1   |       |        |     |     |

|                | 3           |     |        |         |     |       |       |     |        |        |        |     |     | 1     | 1      | 1   | 1   |

The following table lists the auxiliary input signals (or auxiliary I/O signals set to input) that can be rerouted onto output signals and the output signals onto which they can be rerouted.

|                                           |             |                  |               |     |                |    |   |    | LVE            | )S c | am. | ctrl |                |     |   |      |     |     |        |              |          |          | T      | ΓL A      | ux I/    | /0     |        |           |        |         | LV            | IDS I          | Aux C          | )ut            |

|-------------------------------------------|-------------|------------------|---------------|-----|----------------|----|---|----|----------------|------|-----|------|----------------|-----|---|------|-----|-----|--------|--------------|----------|----------|--------|-----------|----------|--------|--------|-----------|--------|---------|---------------|----------------|----------------|----------------|

|                                           |             |                  |               |     | ra Li<br>ector |    |   |    | ra Li<br>ector |      |     |      | ra Li<br>ector |     |   | amei |     |     |        |              |          | A        | ux I   | /O C      | onn      | ecto   | or     |           |        |         |               |                | k I/O<br>necto | r              |

|                                           |             |                  | ֓֟֟֟ <u>֟</u> |     |                |    |   |    |                |      |     |      |                | _   | ` |      |     | •   |        | A            |          |          | C      |           |          | в*     |        |           | D      |         | A             | C              | B*             | D              |

|                                           |             | х                | Г             |     |                |    |   |    |                |      | Г   |      |                |     | Г |      |     |     | 8      | 9            | 2        | 8        | 9      | 3         | 8        | 9      | 2      | 8         | 9      | 3       | 12            | 12             | 13             | 13             |

| M_AUX_IOx or                              |             | v                | 1             | 2   | 3              | 4  | 1 | 2  | 3              | 4    | 1   | 2    | 3              | 4   | 1 | 2    | 3   | 4   | H      |              |          |          |        |           |          |        |        |           |        |         |               | $\vdash$       | $\vdash$       |                |

| M_CC_IOy<br>for M_DEVz <sup>†</sup>       |             | z                | 0             | 0   | 0              | 0  | 1 | 1  | 1              | 1    | 2   | 2    | 2              | 2   | 3 | 3    | 3   | 3   | 0      | 0            | 0/1      | 1        | 1      | 0/1       | 2        | 2      | 2/3    | 3         | 3      | 2/3     | 0             | 1              | 2              | 3              |

| IOI III_DEV2                              |             |                  | H             |     |                |    |   |    |                |      |     |      |                |     | H |      |     |     | H      |              |          |          |        |           |          |        |        |           |        |         | _             | 2              | က္သ            | Ξ.             |

|                                           |             | bath             |               |     |                |    |   |    |                |      |     |      |                |     |   |      |     |     | 4-     | 5            | 9        | _12      | 133    | _14       | _20      |        | _22    | _28       | _29    | 30      | )<br>L        |                | OUT2           | DUT:           |

| Auxiliary input                           | <u> ĕ</u> , | Ē                | ည             | CC2 | CC3            | 50 | 5 | 22 | CC3            | 55   | 5   | CC2  | င္ဌ            | CC4 | 5 | CC2  | င္ပ | 664 | AUX_10 | $\geq$       | AUX_10_6 | JAUX_10_ | AUX_10 | AUX_10_14 | _AUX_10_ | AUX_10 | AUX_10 | AUX_10_28 | AUX_10 | AUX_10_ | $\preceq$     | Σ              | Σ              | ×              |

| signal (or auxiliary<br>I/O signal set to | M_AUX_10x   | Acquisition path | Γ             | Ī   |                | _  |   | _  | Ī              |      |     | _    | _              | Ī   |   |      |     |     | AU     | TTL_AUX_10_5 | 1 1      |          |        |           | AU       |        |        | AU        | JAU    | AU      | LVDS_AUX_OUT7 | LVDS_AUX_OUT15 | LVDS_AUX_OUT23 | LVDS_AUX_OUT31 |

| input)                                    | Σ̈́         | Ā                |               |     |                |    |   |    |                |      |     |      |                |     |   |      |     |     | E      | E            | Ĕ        | Ĕ        | Ę,     | ľ         | Ę        | Ę'     | Ę.     | Ę'        | Ę'     | Ę'      | ואנ           | ĭ              | Z              | N              |

| TTL_AUX_IO_4                              | 8           | 0                | Ŀ             | •   | •              | •  |   |    |                |      |     |      |                |     | L |      |     |     |        |              |          |          |        |           |          |        |        |           |        |         |               |                |                |                |

| TTL_AUX_IO_5                              | 9           | 0                |               |     |                |    |   |    |                |      |     |      |                |     | L |      |     |     |        |              |          |          |        |           |          |        |        |           |        |         |               |                |                |                |

| TTL_AUX_IO_6                              | 2           | 0/1              | Ŀ             | •   | •              | •  | ٠ | •  | •              | •    |     |      |                |     | L |      |     |     |        |              |          |          |        |           |          |        |        |           |        |         |               |                |                |                |

| TTL_AUX_IO_12                             | 8           | 1                |               |     |                |    | ٠ | •  | •              | •    |     |      |                |     | L |      |     |     |        |              |          |          |        |           |          |        |        |           |        |         |               |                |                |                |

| TTL_AUX_IO_13                             | 9           | 1                |               |     |                |    |   |    |                |      |     |      |                |     |   |      |     |     |        |              |          |          |        |           |          |        |        |           |        |         |               |                |                |                |

| TTL_AUX_IO_14                             | 3           | 0/1              |               |     |                |    |   |    |                |      |     |      |                |     |   |      |     |     |        |              |          |          |        |           |          |        |        |           |        |         |               |                |                |                |

| TTL_AUX_IO_20*                            | 8           | 2                |               |     |                |    |   |    |                |      | ١•  | •    | •              | •   |   |      |     |     |        |              |          |          |        |           |          |        |        |           |        |         |               |                |                |                |